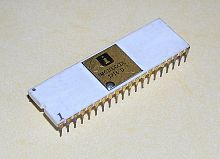

Intersil 6100

The Intersil 6100, or IM6100, is a single-chip microprocessor implementation of the 12-bit PDP-8 instruction set, along with a range of peripheral support and memory ICs developed by Intersil in the mid-1970s. It was sometimes referred to as the CMOS-PDP8. Since it was also produced by Harris Corporation, it was also known as the Harris HM-6100. The Intersil 6100 was introduced in the second quarter of 1975,[1][2] and the Harris version in 1976.[2]

The 6100 family was produced using CMOS rather than the bipolar and NMOS technologies used by most of its contemporaries (Z80, 8080, 6502, 6800, 9900, etc.). As a result of its CMOS technology and low clock speeds, 8 MHz for the Harris HM-6100A, it had relatively low power consumption, less than 100 mW at 10 V/2 MHz, and could be operated from a single supply over the wide range of 4–11 V. Thus, it could be used in high reliability embedded systems without the need for any significant thermal management, if the rest of the system was also CMOS.

The 6100 was available to military specification, and since it was dual sourced by Intersil and Harris, it was used in some military products as a low power alternative to the 8080, 6800 etc. Although it had a very simple instruction set and architecture, it was eminently suitable for use in embedded systems that had previously used discrete logic circuits and even Ledex motorised rotary switches or relay-based logic controllers.

The 6100 family was used in a number of commercial products, including the DECmate line, DEC's first attempt to produce a personal computer. The Intersil 6100 was first used, according to Byte magazine, in Pacific Cyber/Metrix's PCM-12 in 1976.[3] Intersil sold the integrated circuits commercially through 1982 as the IM6100 family. It was not priced competitively, and the offering failed. The IBM PC in 1981 cemented the doom of the "CMOS-8s".

Description

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The 6100 is a 12-bit CPU that closely emulates the PDP-8 (See PDP-8 for a more complete discussion). It has three primary registers: PC (program counter), 12-bit AC (accumulator), and MQ (Multiplier Quotient). All two-operand instructions read the AC and MQ and write back to the AC.

There is no stack pointer; subroutines return to their callers by jumping back into the main code, typically by storing the return address in the first word of the subroutine itself. This makes it difficult to have subroutines in ROM, these must find some other location to store the address. This was not a problem for the original PDP-8, where all main memory was read/write core.

Conditionals in the 6100 allow only the next instruction to be skipped. Branches are constructed with a conditional and a following jump. There is only one maskable interrupt. When the interrupt is tripped, the CPU stores the current PC in 0000, and then starts executing from 0001. The interrupt can be disabled or enabled using the IOF and ION (or SKON) instructions.

The 6100 has a 12-bit data/address bus, limiting RAM to only 4K words, or 6 KB. Memory references are 7-bit, offset either from address 0, or from the PC page base address (obtained by setting the seven least significant bits of PC to zero). Memory could be expanded using the optional 6102 support chip, which added three address lines and thus expanded memory to 32K words (48 KB) in the same way that the PDP-8/E expanded the PDP-8. The 6102 has two internal registers, IFR (instruction field register) and DFR (data field register), that offset the 4K page when the CPU accesses memory.

Versions and supporting hardware

Intersil offered a variety of related chips[4] to support 6100 systems:

- the IM6100 CPU, which implements a straight-8 (basic PDP-8 without memory mapping hardware)

- the IM6101 PIE (Programmable Interface Element) is a basic PDP-8 I/O port

- the IM6102 MEDIC (Memory Extension, DMA Controller, Interval Timer), which converts an IM6100 into something resembling a PDP-8/E's CPU

- the IM6103 PIO (Parallel Input-Output Port), and

- the IM6402 or IM6403 UART - basic PDP-8 I/O devices on ICs.

Intersil also offered compatible sizes of RAM and ROM:

- the IM6551 and IM6561 (1 Kbit, 256×4) SRAM

- the IM6512 (768 Bit, 64x12) SRAM, and

- the IM6312 (12 Kbit, 1024×12) mask programmable PROM.

A selection of these components were offered as parts of the Intersil 6801 CMOS Family Sampler Kit, and with the 6960 Sampler PC Board, a single-board system including the IM6100 CPU, IM6101 PIE, the IM6312 ODT (Octal Debugging Technique) Monitor ROM, three 256×4 CMOS RAMs and a IM6403 UART.

The basic 6100 was later upgraded to the 6120, with the 6102 memory controller built-in.

References

- ^ "The Explosion 1975-1976 » AntiqueTech". AntiqueTech.com. 2009-04-21. Archived from the original on 2017-07-03. Retrieved 2017-06-19.

- ^ a b Bell, Gordon (1980), Family Tree of Digital's Computers, (Poster), Digital Equipment Corporation, retrieved 2017-06-19

- ^ Staff writer (March 1976). "The First of the 12-Bit Micros?". Byte (7). Byte Publications: 88 – via the Internet Archive.

- ^ Intersil (1981). "8. Digital §Microprocessor, Peripherals, Development System". Data Book (PDF). pp. 8-77–8-211.

External links

- "Intersil 6100 microprocessor architecture", CPU World

- Intersil, "IM6100 CMOS Family Sampler" Archived 2014-10-02 at the Wayback Machine