Intel Xeon (Broadwell)

| << Intel Xeon >> | |

|---|---|

| Produktion: | seit 2015 |

| Produzent: | Intel |

| Prozessortakt: | 1,6 GHz bis 3,5 GHz |

| QPI-Takt: | 4,8 GT/s bis 9,6 GT/s |

| L3-Cachegröße: | 6 MiB bis 55 MiB |

| Befehlssatz: | x86/Intel 64 (AMD64) |

| Mikroarchitektur: | Intel-Broadwell-Mikroarchitektur |

| Sockel: | Sockel 2011-3, Sockel 1150 |

| Name des Prozessorkerns: | Broadwell-EX |

Die Intel-Xeon-Serie auf Basis der Intel-Broadwell-Mikroarchitektur ist eine Familie von 64-Bit-Mikroprozessoren für Server und Workstations von Intel. Diese Mehrkernprozessoren mit zwei bis 24 Kernen stellen die Nachfolger der Core-basierten Xeon-Prozessoren dar.

Es werden drei sehr unterschiedliche CPU-Familien hergestellt:

- Xeon D für Mikroserver mit integrierter Peripherie (SoC oder System-on-a-Chip), vier bis 16 Cores, 1,5 MB 3rd Level Cache je Core, zwei DDR4-Kanäle

- Xeon E3 für Einprozessorsysteme mit integrierter Prozessorgrafik, vier Cores, 1,5 MB 3rd Level Cache je Core, zwei DDR4-RAM-Kanäle

- Xeon E5- und E7 für NUMA-Mehrprozessorsysteme mit QPI-Verbindungen, vier bis 22 Cores, 2,5 MB 3rd Level Cache je Core, vier DDR4-RAM-Kanäle

Die Xeons der Broadwell-Generation unterstützen nun DDR4-Speichermodule auf vier Speicherkanälen. Ein Prozessor kann damit in bis zu zwölf DIMM-Steckplätzen (abhängig von der Größe der verfügbaren Module) bis zu 1536 GByte Arbeitsspeicher unterstützen.

- Der Xeon D-Chip (4 bis 8 Cores) hat eine Größe von 14,76 mm × 10,85 mm – 160,24 mm²[1]

Die E5 und E7-Varianten werden auch Broadwell-EP/EX genannt. Der Chip wird in drei Varianten gefertigt:

- "LCC": Low Core Count, 16,2 mm × 15,2 mm – 246,24 mm² – 3,2 Mrd. Transistoren – 10 Kerne

- "MCC": Mid Core Count, 16,2 mm × 18,9 mm – 306,18 mm² – 4,7 Mrd. Transistoren – 15 Kerne

- "HCC": High Core Count, 18,1 mm × 25,2 mm – 456,12 mm² – 7,2 Mrd. Transistoren – 24 Kerne

Broadwell-EP/EX HCC

Bild von Intel

Link zum Bild

(Bitte Urheberrechte beachten)

Die verkauften Varianten entstehen durch Test und Selektion; damit der Ausschuss in der Fertigung nicht zu hoch ist, müssen nicht alle Kerne funktionsfähig sein und werden gegebenenfalls abgeschaltet. Die Kerne sind mit bidirektionalen Ring-Bussen untereinander und mit dem 3rd-Level-Cache-Arbeitsspeichersystem verbunden. Im Kernbereich befinden sich 256 kB 2nd-Level- und 32 kB 1st-Level-Cachespeicher, Außerhalb der Kerne befinden sich 2,5 MB je Kern im 3rd-Level-Cachespeicher, sowie die Controller für QPI-Ports, DDR-RAM und PCI E 3.0.

Modelle

Es existiert eine Vielzahl von Modellen. Die Haupt-Parameter sind:

- Die erste Ziffer des vierstelligen Produktcodes gibt an, wie viele Prozessoren dieses Typs auf einer Hauptplatine parallel genutzt werden können (Anzahl der Sockel im Gegensatz zu Anzahl Cores).

- Taktfrequenz (geht direkt in die Single-Task-Leistung ein und ist für viele Programme leistungsbestimmend)

- Cachegröße (erhöht den Datendurchsatz)

- Anzahl Cores (erhöht die Anzahl der gleichzeitig bearbeitbaren Tasks)

- Thermal Design Power: Verlustleistung, begrenzt den Einsatzzweck, je höher, desto größer müssen Kühlsystem und Spannungsversorgung dimensioniert sein, geht mit der Taktfrequenz, der Anzahl der Cores und der Größe des Caches in die Höhe. Die Modelle mit einem "L" hinter dem 4-stelligen Produktcode sind Low Power-Versionen mit geringerem Energieverbrauch für Microserver

- integrierte GPU: nur für Workstations mit geringer 3D-Grafikleistung interessant (siehe auch Intel HD Graphics), da in CAD-Workstations in der Regel Grafik-Beschleuniger mit hoher Rechenleistung zusätzlich gesteckt werden

Xeon D-15xx

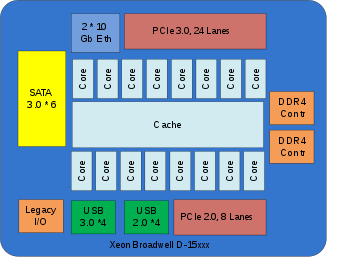

Intel brachte Anfang 2015 eine Reihe von „SoC“ (System on a Chip)-Varianten heraus, die Xeon D-Reihe, die als CPUs mit integriertem Chipsatz (Peripherieanschlüsse wie PCI, USB, SATA und Ethernet) für Mikroserver gedacht sind. Diese CPUs werden nicht über den Stecksockel Sockel 2011-3 der E3, E5, E7 v4-Reihen, sondern über einen FCBGA 1667 genannten Ball-Grid-Array-Lötsockel fest mit der Hauptplatine verbunden. Die CPUs unterstützen nur zwei Arbeitsspeicherkanäle anstelle von vier in den großen v4-Varianten und nur eine CPU je System. Sie werden augenscheinlich gegen neu entwickelte Server-CPUs mit ARM-Architektur positioniert.

Bild: Blockschaltbild einer Xeon D-15xx CPU

| Produktcode | L3-Cache | Takt | Release | Cores | TDP | integrierte GPU |

|---|---|---|---|---|---|---|

| D-1518 | 6 MB | 2,20 GHz | Q4'15 | 4 | 35 W | keine |

| D-1521 | 6 MB | 2,40 GHz | Q4'15 | 4 | 45 W | keine |

| D-1527 | 6 MB | 2,20 GHz | Q4'15 | 4 | 35 W | keine |

| D-1528 | 9 MB | 1,90 GHz | Q4'15 | 6 | 35 W | keine |

| D-1529 | 6 MB | 1,30 GHz | Q2'16 | 4 | 20 W | Keine |

| D-1531 | 9 MB | 2,20 GHz | Q4'15 | 6 | 45 W | keine |

| D-1537 | 12 MB | 1,70 GHz | Q4'15 | 8 | 35 W | keine |

| D-1539 | 12 MB | 1,60 GHz | Q2'16 | 8 | 35 W | keine |

| D-1541 | 12 MB | 2,10 GHz | Q4'15 | 8 | 45 W | keine |

| D-1548 | 12 MB | 2,00 GHz | Q4'15 | 8 | 45 W | keine |

| D-1577 | 24 MB | 1,30 GHz | Q1'16 | 16 | 45 W | keine |

| D-1567 | 18 MB | 2,10 GHz | Q1'16 | 12 | 65 W | keine |

| D-1559 | 18 MB | 1,50 GHz | Q2'16 | 12 | 45 W | keine |

| D-1571 | 24 MB | 1,30 GHz | Q1'16 | 16 | 45 W | keine |

| D-1557 | 18 MB | 1,50 GHz | Q1'16 | 12 | 45 W | keine |

Im Folgenden die CPU-Varianten ohne integrierte Peripherie.

E3 v4 für Einprozessorsysteme

Die E3-1xxx-v4-Varianten besitzen nur zwei Hauptspeicherkanäle und keine QPI-Links, da sie für Ein-Sockel-Systeme gebaut sind. Die CPUs führen 16 PCIe-3.0-Lanes in das System heraus.

Deshalb benötigen sie auch nicht den Sockel 2011v3, sondern kommen mit einem Sockel 1150 aus. Nachfolgend ein Blockschaltbild eines typischen E3-Systems:

| Produktcode | L3-Cache | Takt | Release | Cores | TDP | integrierte GPU |

|---|---|---|---|---|---|---|

| E3-1285L v4 | 6 MB | 3,40 GHz | Q2'15 | 4 | 65 W | Intel Iris Pro Graphics P6300 |

| E3-1285 v4 | 3,50 GHz | 95 W | ||||

| E3-1278L v4 | 2,00 GHz | 47 W | ||||

| E3-1265L v4 | 2,30 GHz | 35 W | ||||

| E3-1258L v4 | 1,80 GHz | 47 W | Intel HD Graphics P5700 |

Broadwell EP/EX – die E5v4- und E7v4-Familien

Die E5-Varianten (26xx und 46xx) sind mit zwei QPI-Links für die Sockel-zu-Sockel-Verbindungen ausgestattet, die E7-Varianten (48xx und 88xx) sind mit drei QPI-Links ausgestattet. E5- und E7-Varianten besitzen vier DDR4-Hauptspeicherkanäle und führen 40 PCIe-3.0-Lanes in das System heraus. Nachfolgend ein Blockschaltbild eines E5-26xx-Systems:

| Produktcode | L3-Cache | Takt | Release | Cores | TDP |

|---|---|---|---|---|---|

| E5-2699 v4 | 55 MB | 2,20 GHz | Q1'16 | 22 | 145 W |

| E5-2695 v4 | 45 MB | 2,10 GHz | Q1'16 | 18 | 120 W |

| E5-2660 v4 | 35 MB | 2,00 GHz | Q1'16 | 14 | 105 W |

| E5-2680 v4 | 35 MB | 2,40 GHz | Q1'16 | 14 | 120 W |

| E5-2683 v4 | 40 MB | 2,10 GHz | Q1'16 | 16 | 120 W |

| E5-2687W v4 | 30 MB | 3,00 GHz | Q1'16 | 12 | 160 W |

| E5-2690 v4 | 35 MB | 2,60 GHz | Q1'16 | 14 | 135 W |

| E5-2697 v4 | 45 MB | 2,30 GHz | Q1'16 | 18 | 145 W |

| E5-2697A v4 | 40 MB | 2,60 GHz | Q1'16 | 16 | 145 W |

| E5-2698 v4 | 50 MB | 2,20 GHz | Q1'16 | 20 | 135 W |

| E5-2658 v4 | 35 MB | 2,30 GHz | Q1'16 | 14 | 105 W |

| E5-2650L v4 | 35 MB | 1,70 GHz | Q1'16 | 14 | 65 W |

| E5-2650 v4 | 30 MB | 2,20 GHz | Q1'16 | 12 | 105 W |

| E5-2648L v4 | 35 MB | 1,80 GHz | Q1'16 | 14 | 75 W |

| E5-2628L v4 | 30 MB | 1,90 GHz | Q1'16 | 12 | 75 W |

| E5-2630L v4 | 25 MB | 1,80 GHz | Q1'16 | 10 | 55 W |

| E5-2667 v4 | 25 MB | 3,20 GHz | Q1'16 | 8 | 135 W |

| E5-2623 v4 | 10 MB | 2,60 GHz | Q1'16 | 4 | 85 W |

| E5-2630 v4 | 25 MB | 2,20 GHz | Q1'16 | 10 | 85 W |

| E5-2618L v4 | 25 MB | 2,20 GHz | Q1'16 | 10 | 75 W |

| E5-2637 v4 | 15 MB | 3,50 GHz | Q1'16 | 4 | 135 W |

| E5-2640 v4 | 25 MB | 2,40 GHz | Q1'16 | 10 | 90 W |

| E5-2620 v4 | 20 MB | 2,10 GHz | Q1'16 | 8 | 85 W |

| E5-2608L v4 | 20 MB | 1,60 GHz | Q1'16 | 8 | 50 W |

| E5-2643 v4 | 20 MB | 3,40 GHz | Q1'16 | 6 | 135 W |

| E5-2609 v4 | 20 MB | 1,70 GHz | Q1'16 | 8 | 85 W |

| E5-2603 v4 | 15 MB | 1,70 GHz | Q1'16 | 6 | 85 W |

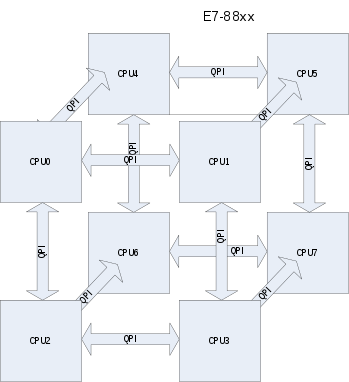

Die QPI-Links bilden die Verschaltung zwischen den Hauptspeicherkontrollern der unterschiedlichen CPUs zu einem Non-Uniform Memory Access-Rechner: der Zugriff auf die vier lokalen Speicherkanäle einer CPU ist schneller, als der über QPI auf die entfernten Speicherkanäle anderer CPUs.

In einem Acht-CPU-System werden drei CPUs direkt über einen QPI-Link erreicht, drei weitere CPUs (über je zwei mögliche Wege) über eine Vermittler-CPU, die letzte diametrale CPU (über je sechs mögliche Wege) über zwei Vermittler-CPUs.

| Produktcode | L3-Cache | Takt | Release | Cores | TDP |

|---|---|---|---|---|---|

| E5-4669 v4 | 55 MB | 2,20 GHz | Q2'16 | 22 | 135 W |

| E5-4667 v4 | 45 MB | 2,20 GHz | Q2'16 | 18 | 135 W |

| E5-4660 v4 | 40 MB | 2,20 GHz | Q2'16 | 16 | 120 W |

| E5-4655 v4 | 30 MB | 2,50 GHz | Q2'16 | 8 | 135 W |

| E5-4650 v4 | 35 MB | 2,20 GHz | Q2'16 | 14 | 105 W |

| E5-4640 v4 | 30 MB | 2,10 GHz | Q2'16 | 12 | 105 W |

| E5-4627 v4 | 25 MB | 2,60 GHz | Q2'16 | 10 | 135 W |

| E5-4620 v4 | 25 MB | 2,10 GHz | Q2'16 | 10 | 105 W |

| E5-4610 v4 | 25 MB | 1,80 GHz | Q2'16 | 10 | 105 W |

| E5-4628L v4 | 35 MB | 1,80 GHz | Q2'16 | 14 | 75 W |

| E7-4809 v4 | 20 MB | 2,10 GHz | 6. Jun. 2016 | 8 | 115 W |

| E7-4820 v4 | 25 MB | 2,00 GHz | 6. Jun. 2016 | 10 | 115 W |

| E7-4830 v4 | 35 MB | 2,00 GHz | 6. Jun. 2016 | 14 | 115 W |

| E7-4850 v4 | 40 MB | 2,10 GHz | 6. Jun. 2016 | 16 | 115 W |

| E7-8893 v4 | 60 MB | 3,20 GHz | 6. Jun. 2016 | 4 | 140 W |

| E7-8891 v4 | 60 MB | 2,80 GHz | 6. Jun. 2016 | 10 | 165 W |

| E7-8860 v4 | 45 MB | 2,20 GHz | 6. Jun. 2016 | 18 | 140 W |

| E7-8867 v4 | 45 MB | 2,40 GHz | 6. Jun. 2016 | 18 | 165 W |

| E7-8870 v4 | 50 MB | 2,10 GHz | 6. Jun. 2016 | 20 | 140 W |

| E7-8880 v4 | 55 MB | 2,20 GHz | 6. Jun. 2016 | 22 | 150 W |

| E7-8890 v4 | 60 MB | 2,20 GHz | 6. Jun. 2016 | 24 | 165 W |

| E7-8891 v4 | 60 MB | 2,80 GHz | Q2, 2016 | 10 | 165 W |

| E7-8893 v4 | 60 MB | 3,20 GHz | Q2, 2016 | 4 | 140 W |

| E7-8894 v4 | 60 MB | 2,40 GHz | Q1, 2017 | 24 | 165 W |

Siehe auch

Einzelnachweise

- ↑ SemiAccurate: Xeon D-1500 Line SemiAccurate: Xeon D-1500 Line, Artikel vom 9. März 2015